# Universidade Federal do Rio Grande do Norte Centro de Tecnologia Programa de Pós-Graduação em Engenharia Elétrica e de Computação

# Projeto em FPGA de um Controlador Unificado para Correção de Fator de Potência com Retificadores *Boost* Bidirecionais Monofásicos

#### **Antonio Wallace Antunes Soares**

Orientador: Prof. Dr. Aluizio Alves de Melo Bento

**Dissertação de Mestrado** apresentada ao Programa de Pós-Graduação em Engenharia Elétrica e de Computação da UFRN (área de concentração: Automação e Sistemas) como parte dos requisitos para obtenção do título de Mestre em Ciências.

Natal, RN, 18 de dezembro de 2013.

#### UFRN / Biblioteca Central Zila Mamede Catalogação da Publicação na Fonte

Soares, Antonio Wallace Antunes

Projeto em FPGA de um controlador unificado para correção de fator de potência em retificadores boost bidirecionais monofásicos. / Antonio Wallace Antunes Soares. – Natal, RN, 2013.

81 f.; il.

Orientador: Prof. Dr. Aluizio Alves de Melo Bento.

Dissertação (Mestrado) — Universidade Federal do Rio Grande do Norte. Centro de Tecnologia. Programa de Pós-Graduação Engenharia Elétrica e da Computação.

1. Eletrônica de potência — Dissertação. 2. Correção de fator de potência — Dissertação. 3. One-cycle control technique — Dissertação. 4. Retificadores boost — Dissertação. 5. Conversores intercalados — Dissertação. 6. Controle digital. I. Bento, Aluizio Alves de Melo. II. Universidade Federal do Rio Grande do Norte. III. Título.

RN/UF/BCZM CDU 621.38

## Projeto em FPGA de um Controlador Unificado para Correção de Fator de Potência com Retificadores *Boost* Bidirecionais Monofásicos

#### **Antonio Wallace Antunes Soares**

Dissertação de Mestrado aprovada em 18 de dezembro de 2013 pela banca examinadora composta pelos seguintes membros:

| My DI M. Berl                                                  |

|----------------------------------------------------------------|

| <br>Prof. Dr. Aluizio Alves de Melo Bento (Orientador)DEE/UFRN |

| Prof. Dr. Valentin Obac Roda. DEE/UFRN                         |

| Appan                                                          |

| <br>Prof. Dr. José Alberto Nicolau de OliveiraDEE/UFRN         |

| Carl broke have                                                |

| <br>Prof. Dr. Paulo Peixoto Praça                              |

À minha avó Maria das Graças, aos meus pais Marcílio de Souza e Edineide Antunes, à minha irmã Nadja Raquel e especialmente à minha noiva Dulcinéia Araújo.

# Agradecimentos

Primeiramente, a Deus por me dar forças todos os dias para continuar minha jornada.

À minha família, pelo total apoio dado durante toda minha vida. À minha mãe, Edineide Antunes da Silva, ao meu pai, Marcílio de Souza Soares, à minha avó, Maria das Graças de Souza Soares, à minha irmã, Nadja Raquel Antunes Soares, e em especial à minha noiva e companheira, Dulcinéia Araújo de Lima, pelo apoio e compreensão durante cada etapa da minha vida.

Ao meu orientador, professor Aluizio Alves de Melo Bento, pela dedicada orientação e ajuda ao longo dessa jornada.

Ao professor José Alberto Nicolau de Oliveira, pelo apoio e orientação nos momentos difíceis.

À CAPES, pelo apoio financeiro durante a execução do trabalho.

### Resumo

A utilização de Field Programmable Gate Array (FPGA) para o desenvolvimento de estratégias de controle digital para aplicações em eletrônica de potência tem despertado um crescente interesse entre muitos pesquisadores. Tal interesse se deve as grandes vantagens apresentadas pelo FPGA, que incluem: menor esforço de projeto, alto desempenho e grande flexibilidade de prototipagem. Este trabalho propõe o desenvolvimento e implementação de um controlador unificado, mediante o uso de FPGA, utilizando a técnica de controle de um ciclo (One-Cycle Control Technique) para correção de fator de potência com retificadores boost. Este controlador pode ser aplicado a um total de doze conversores, sendo seis inversores e seis retificadores, definidos pela topologia e pelo tipo de modulação de tensão. As topologias consideradas neste trabalho são: ponte completa, ponte completa intercalada, meia ponte e meia ponte intercalada. Enquanto que as modulações são classificadas em modulação bipolar de tensão (MBT), modulação unipolar de tensão (MUT) e modulação com grampeamento de tensão (MGT). O projeto é desenvolvido e prototipado utilizando as ferramentas Matlab®/Simulink em conjunto com a biblioteca DSP Builder, disponibilizada pela Altera®. O controlador proposto é com resultados de simulação e experimentais.

**Palavras-chave:** Eletrônica de potência; correção de fator de potência; *one-cycle control technique*; retificadores *boost*; conversores intercalados; controle digital; FPGA; DSP Builder.

### **Abstract**

The use of Field Programmable Gate Array (FPGA) for development of digital control strategies for power electronics applications has aroused a growing interest of many researchers. This interest is due to the great advantages offered by FPGA, which include: lower design effort, high performance and highly flexible prototyping. This work proposes the development and implementation of an unified one-cycle controller for boost CFP rectifier based on FPGA. This controller can be applied to a total of twelve converters, six inverters and six rectifiers defined by four single phase VSI topologies and three voltage modulation types. The topologies considered in this work are: full-bridge, interleaved full-bridge, half-bridge and interleaved half-bridge. While modulations are classified in bipolar voltage modulation (BVM), unipolar voltage modulation (UVM) and clamped voltage modulation (CVM). The proposed project is developed and prototyped using tools Matlab/Simulink® together with the DSP Builder library provided by Altera®. The proposed controller was validated with simulation and experimental results.

#### **Keywords:**

Power electronics – power factor correction – one-cycle control technique – boost rectifier – interleaved converters– digital control – FPGA – DSP Builder.

# Sumário

| Sumário                                                   | vii  |

|-----------------------------------------------------------|------|

| Lista de Figuras                                          | ix   |

| Lista de Tabelas                                          | xiii |

| Lista de Símbolos e Abreviaturas                          | xiv  |

| 1 Introdução                                              | 1    |

| 1.1 Motivação                                             | 3    |

| 1.2 Objetivos                                             | 5    |

| 1.3 Contribuições                                         | 5    |

| 1.4 Organização do Trabalho                               | 6    |

| 2 Estado da Arte                                          | 7    |

| 2.1 Controle Digital Aplicado à Eletrônica de Potência    | 7    |

| 2.2 A Técnica de Controle de um Ciclo e suas Aplicações   | 10   |

| 2.3 Síntese do Capítulo                                   | 12   |

| 3 Retificadores <i>Boost</i> Bidirecionais                | 13   |

| 3.1 Topologias                                            | 13   |

| 3.1.1 Função de Transferência dos Retificadores Estudados | 15   |

| 3.1.2 Ondulação da Corrente de Entrada                    | 15   |

| 3.2 Controle                                              | 16   |

| 3.3 Modelo                                                | 20   |

| 3.3.1 Modelagem do Conversor <i>Boost</i>                 | 22   |

| 3.3.2 Linearização do Modelo                              | 24   |

| 3.4 Síntese do Capítulo                                   | 27   |

| 4 Concepção do Controlador Universal em FPGA                   | 29            |

|----------------------------------------------------------------|---------------|

| 4.1 DSP Builder                                                | 29            |

| 4.2 Projeto do Gerador do Sinal Senoidal                       | 32            |

| 4.3 Projeto do Gerador do Sinal Triangular                     | 33            |

| 4.4 Projeto do Controlador PI                                  | 34            |

| 4.4.1 Projeto Utilizando Lugar das Raízes                      | 35            |

| 4.4.2 Discretização do Controlador PI                          | 38            |

| 4.5 Modulador PWM                                              | 40            |

| 4.5.1 Retificador Boost Ponte Completa com Modulação Bipolar o | de Tensão40   |

| 4.5.2 Retificador Boost Ponte Completa com Modulação Unipolar  | r de Tensão42 |

| 4.5.3 Retificador Boost Ponte Completa com Modulação com Gra   | ampeamento de |

| Tensão                                                         | 43            |

| 4.5.4 Retificador Boost Ponte Completa Intercalado com Gran    | mpeamento de  |

| Tensão                                                         | 44            |

| 4.5.5 Retificador Boost Meia Ponte com Modulação Bipolar de Te | ensão45       |

| 4.5.6 Retificador Boost Meia Ponte Intercalado com Modulaç     | ão Bipolar de |

| Tensão                                                         | 46            |

| 4.6 Síntese do Capítulo                                        | 46            |

| 5 Resultados de Simulação e Experimentais                      | 49            |

| 5.1 Correção do Fator de Potência e Controle do Barramento     | 49            |

| 5.1.1 Resultados de Simulações                                 | 49            |

| 5.1.2 Resultados Experimentais                                 | 52            |

| 5.2 Síntese do Capítulo                                        | 57            |

| 6 Conclusões                                                   | 58            |

| 6.1 Conclusões Gerais                                          | 58            |

| 6.2 Propostas de Trabalhos Futuros                             | 60            |

| Referências Bibliográficas                                     | 61            |

# Lista de Figuras

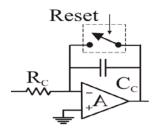

| Figura 2.1: | Integrador de tensão com reset                                                                                                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

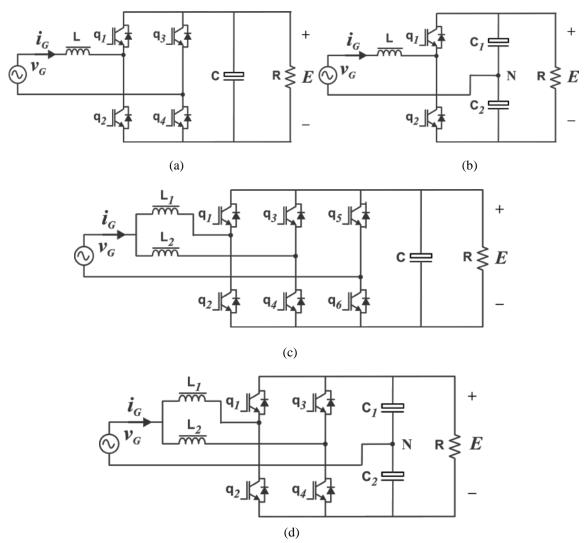

| Figura 3.1: | Topologias CFP Boost. (a) CFP Boost ponte completa; (b) CFP Boost meia ponte; (c) CFP Boost ponte completa intercalada e (d) CFP Boost meia ponte intercalada                                                                              |

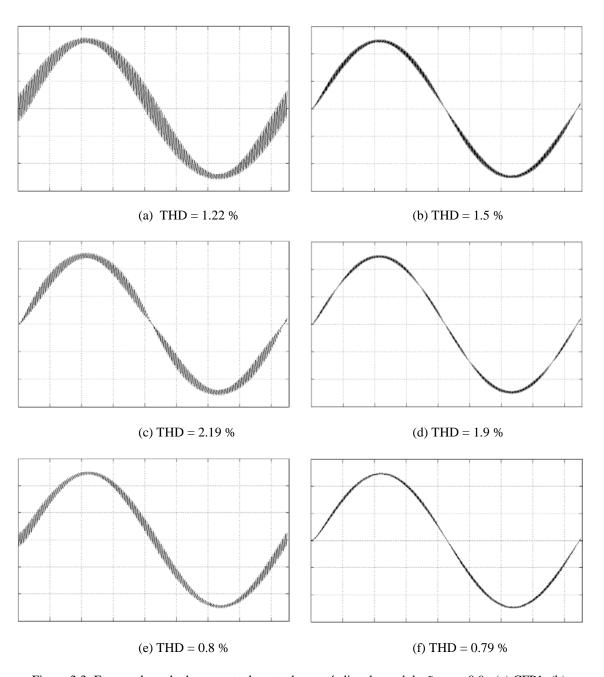

| Figura 3.2  | : Possíveis modulações de tensão para o inversor de tensão em ponte completa. (a) Inversor de tensão em ponte completa, (b) MBT aplicada nas opções CFP1, CFP5 e CFP6; (c) MUT, aplicada na opção CFP2; e (d) MGT, nas opções CFP2 e CFP4. |

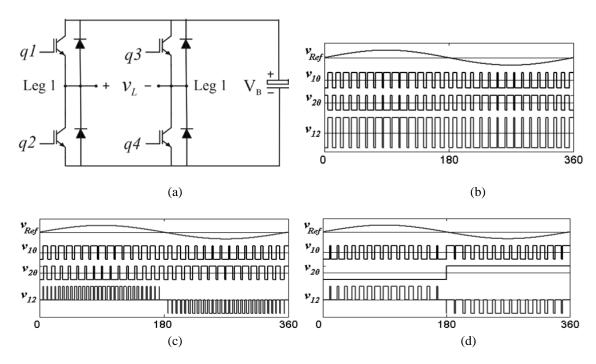

| Figura 3.3: | Formas de onda da corrente de entrada para índice de modulação m = 0,9 (a) CFP1; (b) CFP2; (c) CFP3; (d) CFP4; (e) CFP5; (f) CFP6                                                                                                          |

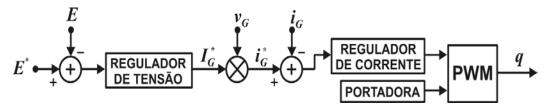

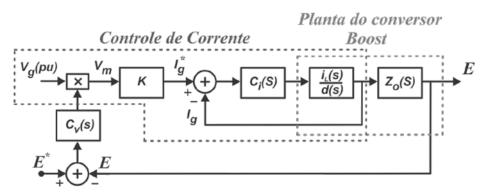

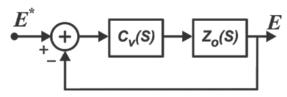

| Figura 3.4: | Esquema da técnica CUC para o controle de corrente                                                                                                                                                                                         |

| Figura 3.5: | Esquema da técnica de controle clássica para o controle de corrente 19                                                                                                                                                                     |

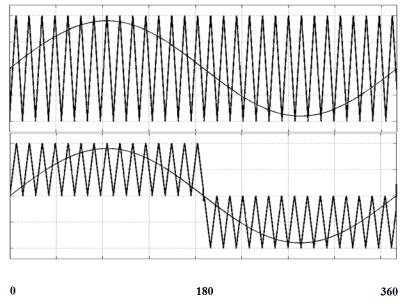

| Figura 3.6: | Sinais de entrada do bloco PWM. Corrente de entrada senoidal e forma de onda das portadoras. Primeiro gráfico: MBT and MUT. Segundo gráfico: MGT                                                                                           |

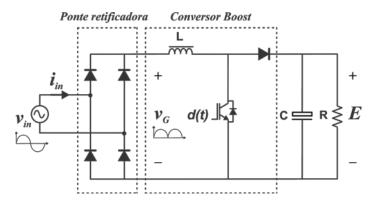

| Figura 3.7: | Estrutura simplificada do retificador boost monofásico unidirecional 21                                                                                                                                                                    |

| Figura 3.8: | Estrutura simplificada conversor boost                                                                                                                                                                                                     |

| Figura 3.9: | Circuito equivalente em modo de condução                                                                                                                                                                                                   |

| Figura 3.10 | 23 Circuito equivalente com chave bloqueada.                                                                                                                                                                                               |

| Figura 3.11 | : Esquema geral do controlador unificado aplicado aos retificadores 28                                                                                                                                                                     |

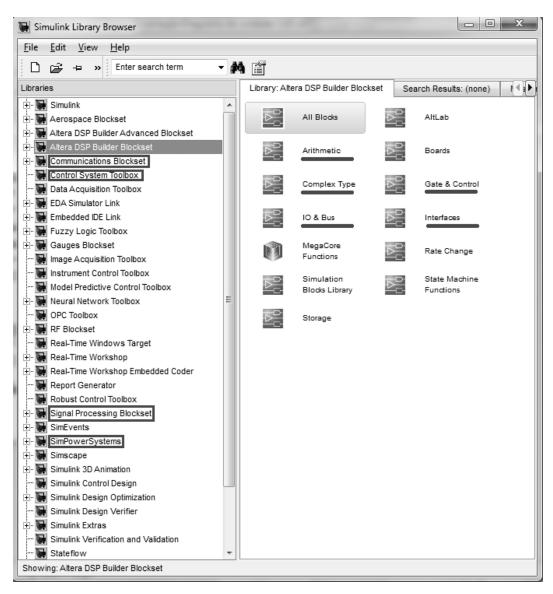

| Figura 4.1: Fluxo de projeto com o DSP Builder                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figura 4.2: Biblioteca DSP builder                                                                                                                                                  |

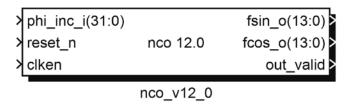

| Figura 4.3: IP NCO megacore function                                                                                                                                                |

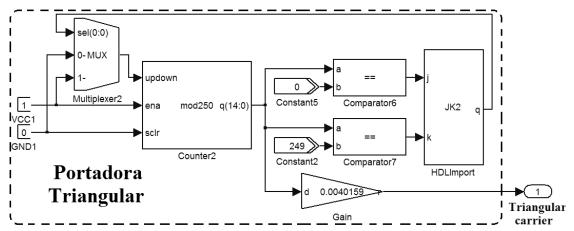

| Figura 4.4: Gerador da portadora triangular                                                                                                                                         |

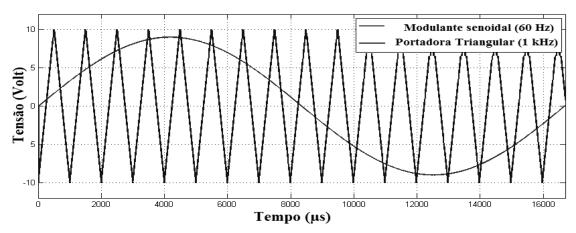

| Figura 4.5: Formas de onda de tensão da portadora triangular e da modulante ou referência senoidal                                                                                  |

| Figura 4.6: Diagrama blocos controle convencional                                                                                                                                   |

| Figura 4.7: Esquema simplificado para controle do barramento                                                                                                                        |

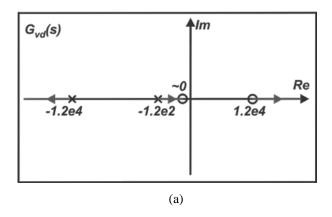

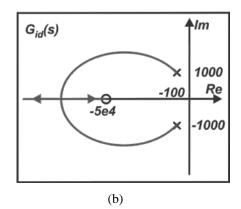

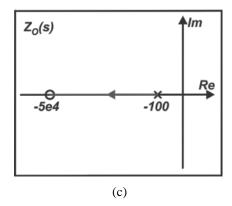

| Figura 4.8: Lugar das raízes para das funções de transferências: (a) $G_{vd}(s)$ , (b) $G_{id}(s)$ e (c) $G_{vi}(s)$                                                                |

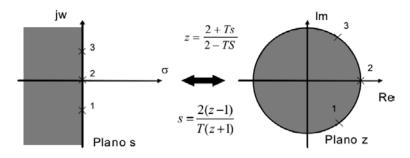

| Figura 4.0.9: Mapeamento do método de discretização bilinear                                                                                                                        |

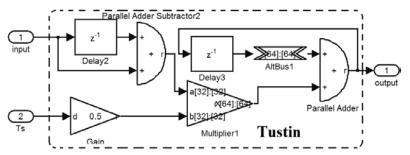

| Figura 4.10: Método Tustin ou Bilinear. 40                                                                                                                                          |

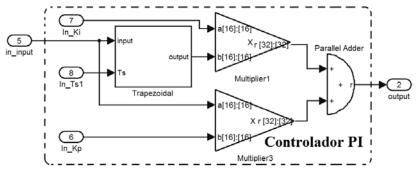

| Figura 4.11: Estrutura completa do controlador PI                                                                                                                                   |

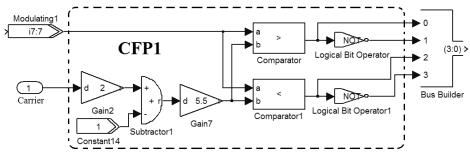

| Figura 4.12: Implementação digital da opção CFP1                                                                                                                                    |

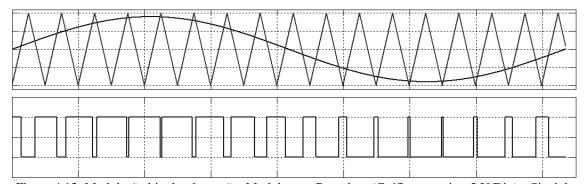

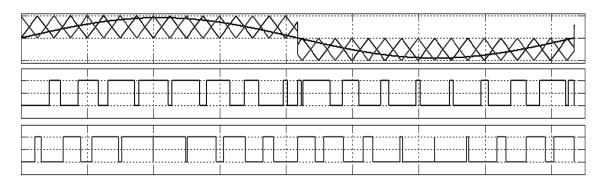

| Figura 4.13: Modulação bipolar de tensão. Modulante e Portadora (Gráfico superior, 3 V/Div) e Sinal de Controle (Gráfico inferior, 1 unidade/Div). Hor.:2ms/div.                    |

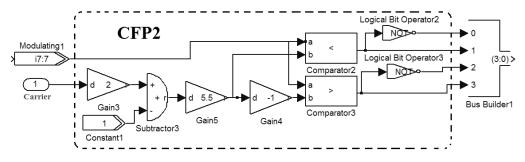

| Figura 4.14: Implementação digital da opção CFP2                                                                                                                                    |

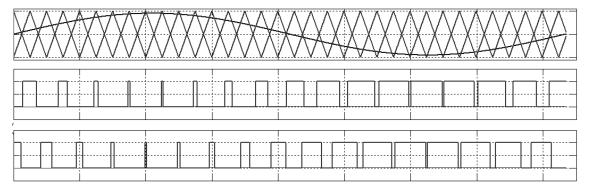

| Figura 4.15: Modulação unipolar de tensão. Modulante e Portadoras (Gráfico superior, 6 V/Div) e Sinais de Controle (Gráfico inferior, 1 unidade/Div). Hor.:2ms/div                  |

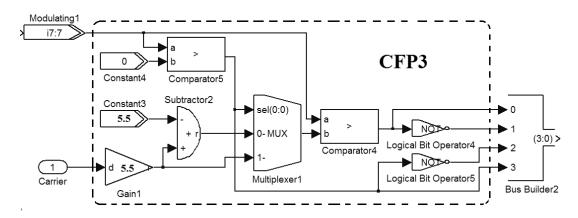

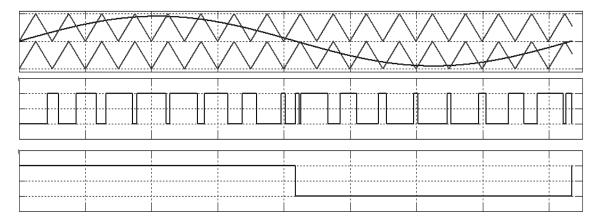

| Figura 4.16: Implementação digital da opção CFP3                                                                                                                                    |

| Figura 4.17: Modulação unipolar com grampeamento de tensão. Modulante e Portadoras (Gráfico superior, 6 V/Div) e Sinais de Controle (Gráfico inferior, 1 unidade/Div). Hor.:2ms/div |

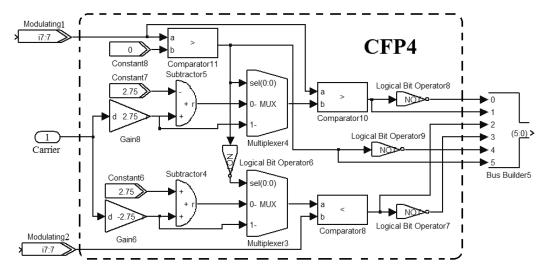

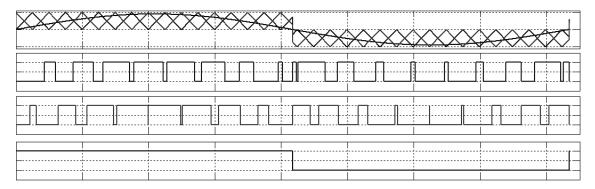

| Figura 4.18: Implementação digital da opção CFP4.                                     | . 45         |

|---------------------------------------------------------------------------------------|--------------|

| Figura 4.19: Modulação com grampeamento de tensão para topologia intercala            | ada          |

| Modulante e Portadoras (Gráfico superior, 3 V/Div) e Sinais de Cont                   | role         |

| (Gráfico inferior, 1 unidade/Div). Hor.:2ms/div                                       | . 45         |

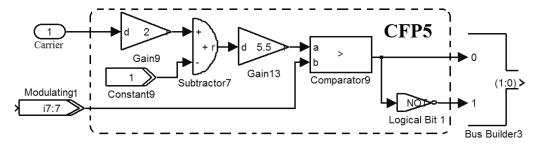

| Figura 4.20: Implementação digital da opção CFP5.                                     | . 45         |

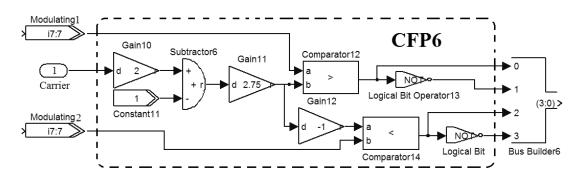

| Figura 4.21: Implementação digital da opção CFP6.                                     | . 46         |

| Figura 4.22: Modulação com grampeamento de tensão para topologia intercalada n        | neia         |

| ponte. Modulante e Portadora (Gráfico superior, 3 V/Div) e Sinal                      | de           |

| Controle (Gráfico inferior, 1 unidade/Div). Hor.:2ms/div                              | . 46         |

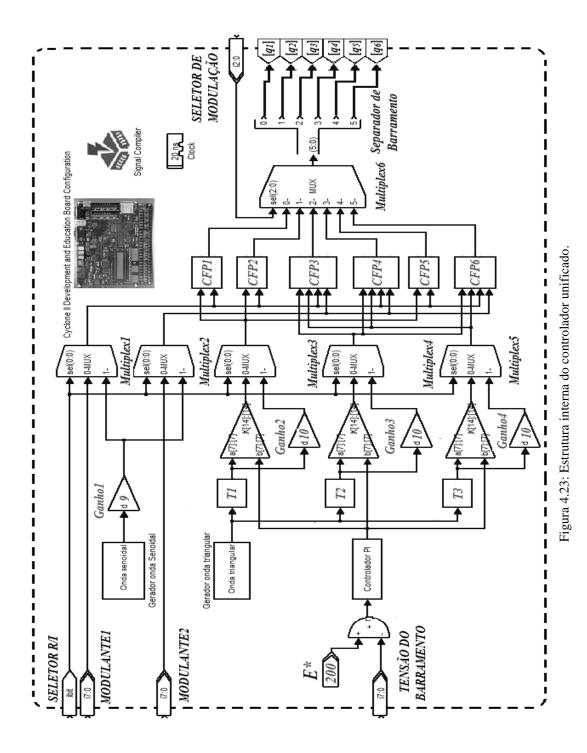

| Figura 4.23: Estrutura interna do controlador unificado.                              | . 48         |

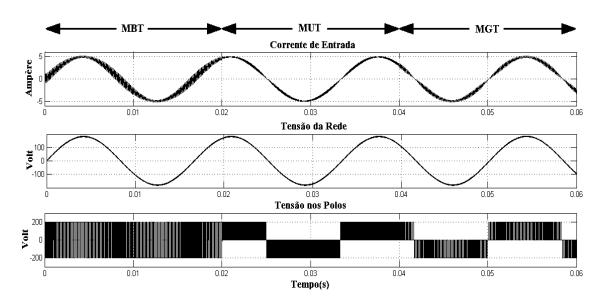

| Figura 5.1: Resultados de simulação para as opções CFP1, CFP2, e CFP3. Grá            | fice         |

| superior: corrente de entrada; Gráfico intermediário: Tensão da re                    | ede          |

| Gráfico inferior: Tensão do polo                                                      | . 50         |

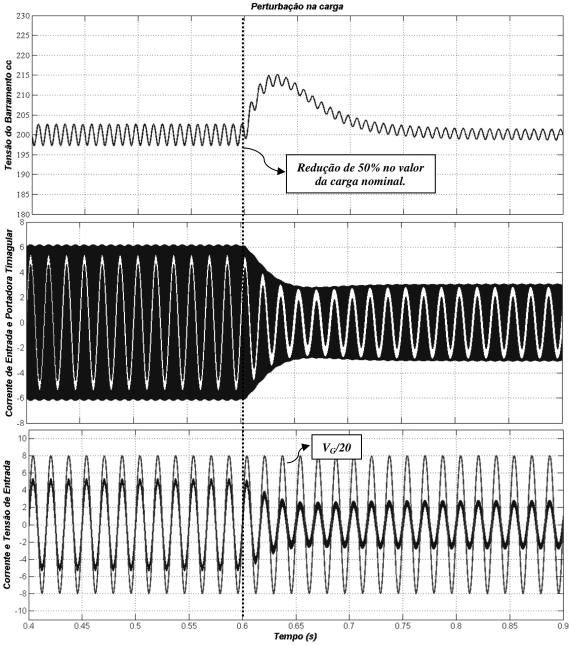

| Figura 5.2: Perturbação na carga.                                                     | . 51         |

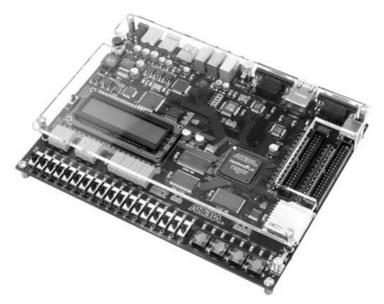

| Figura 5.3: Placa de desenvolvimento DE2 Altera®.                                     | . 52         |

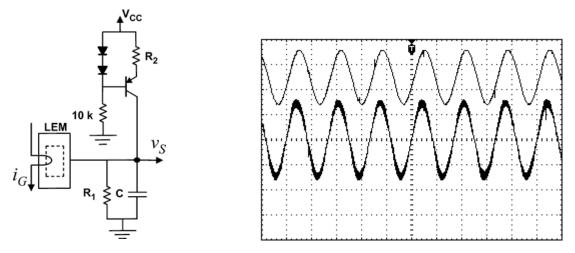

| Figura 5.4: (a) Circuito para processamento de corrente e (b) Corrente de entrada (cu | ırva         |

| inferior, 5 A/Div) e tensão de saída do processador (curva superior                   | r, 1         |

| V/Div). Hor.:10ms/div                                                                 | . 53         |

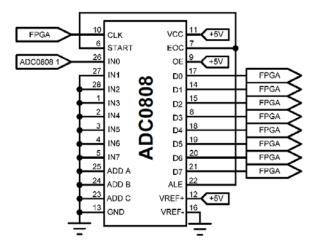

| Figura 5.5: Conversor Analógico/Digital.                                              | . 53         |

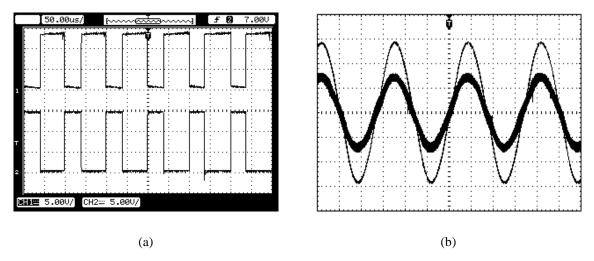

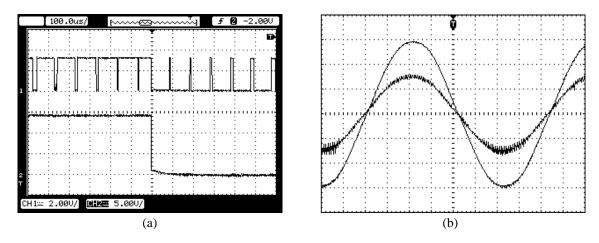

| Figura 5.6: (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 50 Volt/di   | v) e         |

| corrente (menor, 5 A/div) de entrada experimentais para a opção CF                    | ₹ <b>P</b> 1 |

| Hor.:5ms/div.                                                                         | . 55         |

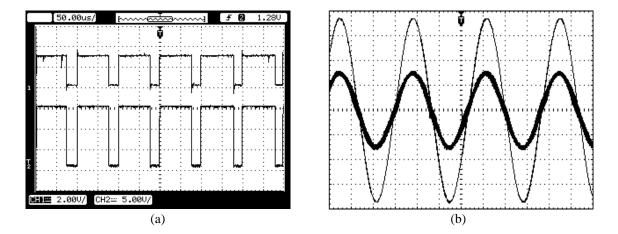

| Figura 5.7: (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 50 Volt/di   | v) e         |

| corrente (menor, 5 A/div) de entrada experimentais para a opção CF                    | ₹P2          |

| Hor.:5ms/div                                                                          | . 55         |

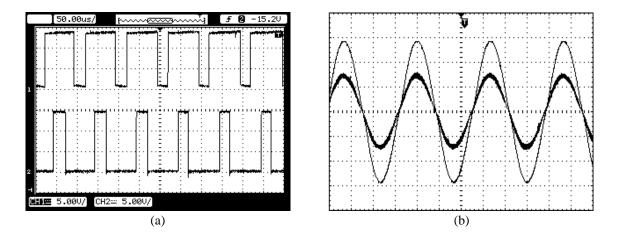

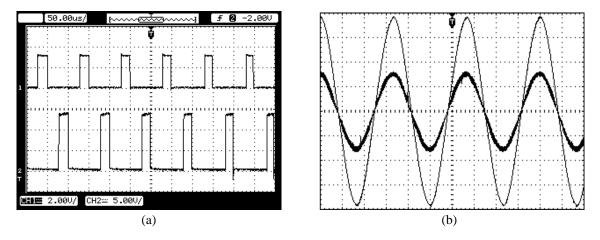

| Figura 5.8: | (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 50 Volt/div) e    |

|-------------|--------------------------------------------------------------------------------|

|             | corrente (menor, 5 A/div) de entrada experimentais para a opção CFP3.          |

|             | Hor.:5ms/div                                                                   |

| Figura 5.9: | (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 50 Volt/div) e    |

|             | corrente (menor, 5 A/div) de entrada experimentais para a opção CFP4.          |

|             | Hor.:2ms/div                                                                   |

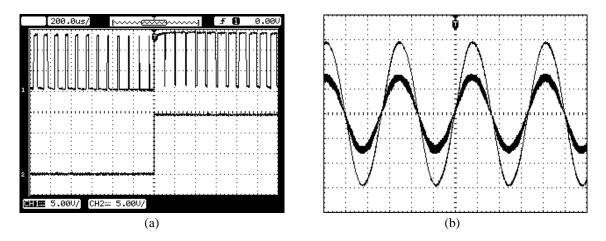

| Figura 5.10 | ): (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 20 Volt/div) e |

|             | corrente (menor, 5 A/div) de entrada experimentais para a opção CFP5.          |

|             | Hor.:5ms/div                                                                   |

| Figura 5.11 | l: (a) Sinais de controle na saída do FPGA e (b) tensão (maior, 20 Volt/div) e |

|             | corrente (menor, 5 A/div) de entrada experimentais para a opção CFP6.          |

|             | Hor.:5ms/div                                                                   |

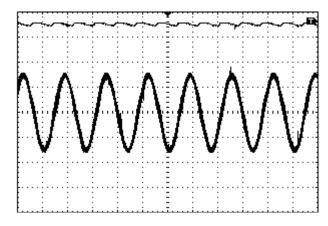

| Figura 5.12 | 2: Tensão do Barramento (Curva Superior, 50V/Div) e Corrente no Indutor        |

|             | (Curva inferior, 5A/Div). Hor.:5ms/div                                         |

# Lista de Tabelas

| Tabela 3.1: Função de transferência de regime quase permanente | 16 |

|----------------------------------------------------------------|----|

| Tabela 3.2: Leis de controle da técnica CUC.                   | 20 |

| Tabela 4.1: Lista de Parâmetros do Modelo Linearizado          | 36 |

| Tabela 4.2: Lista de Parâmetros do Retificador.                | 37 |

| Tabela 5.1: Parâmetros do Modelo                               | 50 |

| Tabela 5.2: Parâmetros Experimentais.                          | 54 |

| Tabela 6.1: Trabalhos publicados                               | 60 |

# Lista de Símbolos e Abreviaturas

ASIC: Application-Specific Integrated Circuit.

CFP1: Retificador boost ponte completa com MBT.

CFP 2: Retificador boost ponte completa com MUT.

CFP 3: Retificador *boost* ponte completa com MGT.

CFP 4: Retificador boost ponte completa intercalado com MGT.

CFP 5: Retificador *boost* meia ponte com MBT.

CFP 6: Retificador *boost* meia ponte com MBT.

CFP: Correção de fator de potência.

CUC: Controle de Um Ciclo.

d: Relação cíclica,  $d=t_{ON}/T_S$ .

E: Tensão cc de saída para retificadores.

$f_G$ : Freqüência da rede.

FPGA: Field Programmable Gate Arrays.

$f_S$ : Frequência de chaveamento.

IP: Intellectual Property.

MBT: Modulação bipolar de tensão.

MGT: Modulação unipolar de tensão com grampeamento.

MUT: Modulação unipolar de tensão.

NCO: Numerically Controlled Oscillator.

PI: Regulador Proporcional e Integral.

PLD: Programmable Logic Device.

$R_e$ : Resistência de entrada equivalente imposta ao retificador.

RMP: Retificador boost meia ponte.

RMPI: Retificador *boost* meia ponte intercalado.

ROM: Read-Only Memory.

RPC: Retificador *boost* ponte completa.

RPCI: Retificador *boost* ponte completa intercalado.

$T_S$ : Período de chaveamento.

# Capítulo 1

# Introdução

Durante as últimas décadas a evolução tecnológica tem propiciado um grande e rápido crescimento da eletrônica de potência. Este crescimento trás como consequência a proposição de várias soluções tecnológicas aplicadas nas mais diversas subáreas da eletrônica de potência, tais como, controle e comando de conversores estáticos, técnicas de acionamento e, principalmente, estruturas de potência. Estas contribuições têm feito da eletrônica de potência uma das áreas de grande importância para evolução da sociedade. Entre seus diversos campos de aplicação pode-se mencionar o campo da qualidade e conservação de energia, o qual tem despertado enorme interesse dos pesquisadores de todo o mundo. Neste campo, busca-se a otimização de circuitos conversores de energia, tentando melhorar sensivelmente a forma de onda da corrente de entrada do sistema elétrico e a frequência distorcida, principalmente devido às cargas não lineares, tais como fontes de alimentação CA-CC, comumente encontradas nos aparelhos eletrônicos existentes, como computadores, aparelhos de som, televisores etc.

A crescente necessidade pela melhoria da eficiência no processamento de energia elétrica tem resultado num grande esforço de pesquisa, culminando no desenvolvimento de inúmeras topologias. Porém nem todas as soluções desenvolvidas são viáveis, tanto economicamente quanto logisticamente. Isto acarreta em uma incessante procura por soluções que apresentem cada vez mais vantagens de ordem prática, baixo custo, pequeno volume e elevada eficiência associada com elevada robustez e confiabilidade, interferindo assim de forma mínima nas fontes de energia e demais equipamentos.

Dentre as diversas topologias aplicadas para qualidade de energia, os retificadores ativos para CFP (Correção de fator de potência) são bastante utilizados. No

que tange aplicação em sistemas monofásicos de média e baixa potência, a adaptação de circuitos conversores *cc-cc* básicos para operação *ca-*cc é um procedimento muito comum na concepção destes retificadores. Entre os conversores básicos destacam-se seis topologias: *Boost*, Cuk, SEPIC, Buck, *Buck-boost* e Zeta (TOLLIK, 1992; SEBASTIAN, 1997; GARCIA, 2001). No caso das três primeiras topologias, a corrente de entrada pode trabalhar de forma ininterrupta, uma vez que há um indutor trabalhando em série com a entrada e a chave é conectada apenas em derivação na saída do indutor. Porém, as demais topologias operam com corrente de entrada pulsante, pois a chave do conversor trabalha em série com a entrada da rede (BENTO, 2009). Estudos demonstraram que o conversor *boost* possui melhor desempenho quando utilizado para CFP, quando comparado com os conversores Cuk e SEPIC, mesmo apresentando problemas como a proteção da carga e a impossibilidade de isolar a saída. Em (HERNÁNDEZ, 1995) o conversor *boost* apresentou maior fator de potência (FP), menor taxa de distorção harmônica total (DHT) e um rendimento maior do que os outros conversores.

Para os retificadores controlados, há inúmeras técnicas de controle para correção de fator de potência, dentre as principais estão a técnica de controle pela corrente média, controle por histerese ou pela corrente de pico. Porém, para grande parte das estratégias de controle, é possível obter uma realização equivalente com a técnica de controle de um ciclo (CUC). Quando comparada com outras estratégias de controle, a CUC apresenta uma série de vantagens, como, por exemplo, supera não linearidades em conversores chaveados, elimina a distorção *crossover*, tem estabilidade em uma ampla variação dinâmica e também não utiliza sensor da tensão da rede (CHAN; ZHAO; QIANG; NENG, 2002). Esta técnica será analisada nos próximos capítulos deste trabalho.

Esta estratégia de controle tem sido comumente implementada analogicamente. Na procura por dispositivos para controle e gerenciamento de sistemas complexos, a gradativa redução do custo e elevação do desempenho dos microcontroladores e dos processadores digitais de sinal (DSP, digital signal processor) torna estes dispositivos bastante atrativos. Com estes dispositivos é possível implementar um sistema de controle e gerenciamento em um único dispositivo, obtendo assim, um sistema mais compacto, flexível, menos susceptível a variações paramétricas e de simples interação. Contudo, ainda é muito comum encontrar unidades de

processamento de energia com conversores estáticos operando com controle analógico (TOROK; MUNK-NIELSON, 2011; BENTO; SANTOS; SILVA, 2006d). Na década de 80, com avanços significativos da eletrônica digital e do microcontroladores, houve uma grande substituição dos controladores analógicos pelos digitais, estendendo a atuação destes dispositivos lógicos, colocando em discussão características como confiabilidade, facilidade de manutenção e flexibilidade para reconfiguração (OGATA, 1995).

É possível observar também que, atualmente, há um grande aumento na utilização de controladores digitais baseados em arranjos de portas lógicas, tendo como principal característica a possibilidade de reconfiguração destes arranjos. Os *chips* como os FPGAs (*Field Programmable Gate Array*) tornam possível a desconsideração de atributos como esforços computacionais e quantidade de espaço para memória de programa, já que sua configuração baseia-se no desenvolvimento de circuitos lógicos digitais que são internamente conectados e cujas funcionalidades são independentes umas das outras (CASTRO; ZUMEL; GARCIA; RIESGO; UCEDA, 2003; GARCIA; ESPI; DEDE; MASET, 2004). É importante comentar, também, que os FPGAs encontrados no mercado têm uma alta densidade de componentes lógicos, possibilitando assim, o controle de vários sistemas e implementações independentes (PERRY, 2002; ORDONEZ; PEREIRA; PENTEADO; PERICINI, 2003).

Diante do que foi introduzido, vale a pena ressaltar e verificar a importância de um controlador digital que possa ser usado em conversores estáticos e que favoreça o avanço da eletrônica de potência, permitindo facilidade de reconfiguração, característica importante na fase de projeto. Neste sentido, as pesquisas atuais exploram a união da eletrônica de potência com o desenvolvimento de novas tecnologias de controle digital (MONMASSON; CIRSTEA, 2007; STR BJ; RN, 1990). Visando sempre propiciar uma maior eficiência do consumo da energia elétrica, uma melhor resposta desses dispositivos e contribuir para uma melhor conservação dos recursos disponibilizados aos consumidores de energia elétrica.

#### 1.1 Motivação

A necessidade real mostra que a busca por estruturas de potência, que apresentem resultados satisfatórios no processamento de energia, dependem, de forma geral, de componentes que tenham grande poder de resposta aliado aos dispositivos com

alto desempenho. Dispositivos estes que compõem o sistema de acionamento da estrutura de potência. Embora soluções comerciais analógicas sejam tipicamente utilizadas em estruturas de controle, o uso do controle digital na eletrônica de potência é uma tendência devido a várias vantagens sobre o controle analógico. Historicamente, soluções analógicas têm as vantagens do baixo custo e da fácil utilização, mas sua principal desvantagem é a falta de flexibilidade.

Hoje, com o aumento do desempenho, redução dos custos dos circuitos digitais, alto nível de integração dos periféricos, imunidade a ruídos, flexibilidade no projeto e na implementação, são alguns dos muitos benefícios de usar controle digital (BEM-YAAKOV; ZELTER, 2006). Contudo, existem algumas limitações e características que devem ser consideradas para concepção do sistema de controle, tais como ruídos de quantização, resolução numérica, atraso unitário, segurador de ordem zero (STR BJ; RN, 1990). É preciso considerar que a maioria dos controles digitais aplicados em eletrônica de potência é feita por processadores digitais de sinal (DSP, digital signal processor) (SHAO-LONG; AI-JUAN, 2006). Tais microprocessadores são usualmente programados em linguagem C ou linguagem assembly, adequadas para algoritmos que são executados de forma sequencial. No entanto, quando várias operações devem ser executadas em paralelo pelo mesmo dispositivo, devem ser tomados cuidados para assegurar o desempenho adequado.

Em contraste, os dispositivos FPGAs (*Field Programmable Gate Arrays*) são componentes digitais que unem a flexibilidade de dispositivos programáveis, tais como dispositivos lógicos programáveis (PLD) e microprocessadores de finalidade geral, com o desempenho do *hardware* para finalidade especifica, como ASIC, (BROWN; REOSE; FRANCIS, 1997). Duas fundamentais características dos FPGAs são a versatilidade e a capacidade de executar diferentes tarefas em paralelo. Estes componentes estão assumindo uma importante função na eletrônica de potência (MONMASSON; CIRSTEA, 2007). Função esta, que vem sendo realizada pelos processadores digitais de sinais, responsáveis pelo controle digital de dispositivos de potência, tais como, conversores, retificadores, e inversores.

Diante do que foi relatado nesta seção, a entusiasmante comparação entre mundo digital e analógico e o poder de paralelismo dos FPGAs, o qual proporciona a possibilidade de realizar o controle de várias estruturas ao mesmo tempo, impulsionaram o desenvolvimento deste trabalho.

#### 1.2 Objetivos

O objetivo principal deste trabalho é propor um controlador digital unificado baseado em FPGA, utilizando a técnica de controle de um ciclo aplicado a retificadores *boost* bidirecionais para correção de fator de potência.

O projeto consiste no controle de quatro diferentes estruturas de retificadores *boost*, do tipo ponte completa, meia ponte, ponte completa intercalada e meia ponte intercalada, estas topologias serão mais detalhadas em um capítulo específico. Este trabalho também considera a possibilidade destes retificadores operarem com três tipos de modulações, as quais incluem a modulação bipolar de tensão (MBT), a modulação unipolar de tensão (MUT) e a modulação unipolar com grampeamento de tensão (MGT). Estas topologias, entre várias aplicações, são amplamente aplicadas para qualidade de energia como correção de fator de potência, filtros ativos de potência e inversores conectados a rede.

Estas quatro topologias e as três modulações aliadas, resultam em doze possíveis combinações de controle, seis combinação para a estrutura de potência operando como retificador e mais seis operando como inversor, já que os retificadores considerados neste trabalho são bidirecionais. Um dos objetivos deste trabalho é realizar comparações nas respostas destas doze topologias com relação à estrutura de controle, o comportamento da corrente de entrada e ao fator de potência.

Implementou-se este controlador utilizando os blocos funcionais do Matlab®/Simulink com o auxílio da biblioteca DSP *Builder* da Altera®. Com o intuito de possibilitar que este controlador possa ser utilizado em qualquer outro sistema embarcado já existente, todos os testes do projeto e as simulações realizadas foram no ambiente Matlab®/Simulink. O desenvolvimento do simulador no Matlab®/Simulink, utilizando-se da biblioteca DSP *Builder*, possibilita que sejam feitas alterações bem como uma posterior síntese e programação em um FPGA.

#### 1.3 Contribuições

As principais contribuições geradas no andamento do mestrado:

- Estudo e projeto de retificadores *boost* básicos e intercalados aliados à técnica de controle de um ciclo.

- Obtenção de um controlador universal que possa atuar em seis diferentes topologias de retificadores *boost* bidirecionais. Este controlador também

- pode ser utilizado como kit didático para controle de estruturas de potência.

- Realização do projeto fazendo uso da biblioteca DSP *Builder*, no intuito de complementar à literatura com relação à concepção de controle digital utilizando FPGA.

#### 1.4 Organização do Trabalho

Esta dissertação está organizada em seis capítulos:

- Capitulo 1: Apresenta-se uma introdução e base para o entendimento do problema, as justificativas e os objetivos.

- Capítulo 2: Será apresentado o estado da arte com os principais trabalhos de controle digital aplicado à eletrônica de potência.

- Capitulo 3: Será apresentada a fundamentação teórica para embasamento sobre as topologias *boost* para correção de fator de potência.

- Capitulo 4: Será apresentada a concepção de projeto do controlador unificador em PFGA.

- Capitulo 5: Serão apresentados os resultados de simulação e experimentais obtidos para as seis topologias.

- Capitulo 6: Serão apresentadas as conclusões e etapas futuras para o avanço do controlador unificado.

# Capítulo 2

### Estado da Arte

Neste capítulo são apresentados alguns dos principais trabalhos relacionados com o tema dessa dissertação. O levantamento do estado da arte é classificado em dois tópicos, o primeiro trata do controle digital aplicado à eletrônica de potência, abordando a evolução do controle digital às mais diversas aplicações em estruturas de potência. Finalmente são apresentados os trabalhos utilizando a técnica de controle de um ciclo, considerando implementação analógica e digital.

#### 2.1 Controle Digital Aplicado à Eletrônica de Potência

Os primeiros estudos relacionados aos sistemas de controle datam do século passado, para controle de velocidade de máquinas a vapor. Nestes sistemas eram utilizados indicadores locais de temperatura e pressão e atuadores pneumáticos de válvulas, e o controle se dava de forma totalmente manual do tipo liga-desliga. Com o advento dos transistores a partir da década de 1940, a eletrônica e suas subáreas não pararam de evoluir, principalmente com o desenvolvimento de transistores cada vez Foi desenvolvimento menores. este que possibilitou introdução microcontroladores e controladores lógicos programáveis nos sistemas de controle, para os mais diversos tipos de aplicações, impulsionando assim, o surgimento do controle digital.

Em seu trabalho, Krein dividiu o controle digital em eletrônica de potência em três gerações (KREIN, 2007). Comumente, classifica-se a primeira geração de controle digital como a fase em que se utilizavam circuitos que combinavam funções analógicas e digitais (TL494 e chips similares). Porém, Krein foi além da definição tradicional, ele definiu a primeira geração como sistemas de controle que utilizam o que

foi chamado de controle de malha externa, realizando um papel de supervisão, configuração e comunição. Uns dos primeiros exemplos da primeira geração de controle digital foram os acionadores de motores. Quando acionadores eletrônicos de velocidades ajustáveis surgiram no final da década de 1970, muitos já tiveram exposições e interações internas regidas pela lógica digital (TEXAS INSTRUMENTS; ANALOG DEVICES). Já a segunda geração, foi classificada em sistemas de controle que utilizam processos digitais de malha interna, incluindo realimentações em tempo discreto e até mesmo processamento digital de sinais. Esta geração é marcada pelo controle digital em tempo real, aplicada, por exemplo, na geração de sinais PWM digitais para o controle de conversores cc-cc (MATSUO, 1989; SANDERS, 1993). Por fim, a terceira geração é caracterizada pelo controle individual das chaves a fim de aumentar o desempenho para além dos limites físicos da eletrônica de potência. O controle de terceira geração é um tema presente em alguns grupos de pesquisa. Um dos primeiros exemplos que segue esta abordagem está em (CELANOVIC, 2000). Muito embora a técnica de controle geométrico utilizada neste trabalho já tenha sido introduzida por (BURNS, 1977), têm-se a observar que não apresentam características da terceira geração, contendo apenas uma análise e representação matemática do assunto.

Recentemente, vários novos métodos de controle digital foram propostos para as mais diversas aplicações em eletrônica de potência, baseados no progresso da tecnologia do processador digital. Pode-se mencionar o acionamento de máquinas, controle de conversores estáticos, inversores, retificadores e filtro ativos de potência. Um exemplo dos métodos empregados atualmente pode ser encontrado em (SHEN, 2012), onde é proposto um novo controle digital de corrente para conversores operando no modo de condução contínua (MCC), onde sua arquitetura é composta por um único indutor e vários estágios de saída. Este método baseia-se no controle preditivo e pode calcular todos os ciclos de trabalho necessários correspondente à saída para o próximo ciclo de chaveamento. Uma vez que o cálculo é feito com o valor instantâneo da corrente de carga, e todos os laços de controle de corrente correspondente às diferentes saídas são independentes, o que pode reduzir significativamente a regulação na passagem por zero.

Já em (SHIN, 2011), é proposto um método de controle digital por corrente média aplicada a retificadores, operando no modo de condução descontínua (MCD),

para correção do fator de potência. Esta técnica de controle proposta não estima, mas monitora a corrente média no indutor em cada ciclo de chaveamento. O método de controle aplicado resultou em uma baixa distorção harmônica (THD de 5%) e em um elevado fator de potência, maior do que as técnicas de controle convencionais, onde o ciclo de trabalho é mantido constante. O protótipo montado opera com uma potência de 200 W e uma frequência de chaveamento de 65 kHz. Para a implementação desta técnica os autores utilizaram um microcontrolador (dsPIC33FJ16GS502). Entre as principais características deste microcontrolador, pode-se ressaltar a presença de dois conversores analógico-digital de 10 bits, com frequência de amostragem de até 4 Msps, fator que possibilita o emprego da técnica de controle em estruturas com alta frequência de chaveamento.

Tratando ainda de aplicações para retificadores, o trabalho realizado por (HWU, 2012) propõe a implementação digital de um controle *fuzzy* aplicado a um retificador trabalhando no MCC, para correção de fator de potência. A principal desvantagem da realização desta técnica, utilizando uma abordagem digital, é a necessidade de vários conversores analógico-digital. Porém, o sinal desejado é obtido através da comparação de duas ondas dente de serra comparadas com o sinal monitorado (através de um sensor hall). Para isto, os autores realizaram a geração de sinais de referência interna ao dispositivo de controle, utilizaram fórmulas matemáticas e algumas informações do comportamento da estrutura (HWU, 2006), como por exemplo, utilizando um comparador para detectar a passagem por zero da tensão de entrada para realização da correção do fator de potência. A eficiência do método proposto foi comprovada com resultados experimentais, através do THD da corrente de entrada e fator de potência, que ficaram em torno de 3% a 12% e de 0.97 a 0.99, respectivamente, dependendo da relação entre a tensão de entrada e a tensão de saída, ou, do índice de modulação.

O FPGA tem se tornado um dispositivo bastante atraente para utilização em sistemas de controle, devido às suas diversas vantagens já mencionadas. Os trabalhos realizados em (CHEN, 2012; NETO, 2013), aplicam diferentes estratégias de controle para a mesma topologia. O primeiro trabalho implementa a técnica de controle por corrente média enquanto o segundo realiza o método de controle robusto. A topologia utilizada para aplicação foi um conversor *boost* cc-cc para correção do fator de potência. Os controladores concebidos nestes trabalhos foram implementados no kit didático da

Altera® DE2 cyclone II, para a aquisição dos sinais empregou-se conversores analógico-digitais externos à placa. Ambos os projetos foram validados com resultados de simulações e experimentais.

Com base nas referências apresentadas nesta seção, pode-se perceber que os trabalhos atuais tendem a fazer uso, principalmente, do controle digital. Além disso, percebe-se também, que há uma gama de aplicações nas quais o controle digital pode ser utilizado, sem comentar a variedade de métodos de controle que podem ser implementados digitalmente, utilizando os mais diferentes dispositivos digitais.

#### 2.2 A Técnica de Controle de um Ciclo e suas Aplicações

Os primeiros estudos referentes à técnica de controle de um ciclo (CUC), foram apresentados por (SMEDLEY, 1995; LAI, 1997), esta estratégia tem se mostrado bastante eficiente para aplicações com correção de fator de potência, pois sua principal característica é fazer com que a relação entre a tensão e a corrente de entrada seja linear. Além disso, o método CUC elimina algumas desvantagens apresentadas na maioria das técnicas propostas, é imune a ruídos e não faz uso de multiplicadores analógicos nem de sensores para tensão da rede (CHAN, 2002; HUA, 2003).

Para as mais diversas técnicas de controle, como por exemplo, para o controle de corrente por histerese, pela corrente de pico e pela corrente média é possível obter uma realização equivalente da técnica CUC, que tem apresentado um grande progresso e um ótimo desempenho no controle de conversores chaveados. Este desempenho se deve ao fato desta técnica emular uma resistência pura vista pela rede e ao fato do controle ser realizado sem o controlador de corrente (malha interna), que é uma característica das técnicas mais difundidas, proporcionando uma resposta rápida e precisa (CHAN, 2002; HUA, 2003; JIN, 2007).

As estratégias de controle geradas com a técnica CUC são facilmente implementadas com controladores analógicos ou digitais (BENTO, 2006). Em aplicações sensíveis à custo, são utilizados, quase que exclusivamente, controladores analógicos (BEN-YAAKOV, 2006), pois os controladores analógicos são de baixo custo, além de não usar multiplicador analógico, nem controlador de corrente, nem sensor de tensão de entrada. No caso de controladores digitais, o processamento fica bastante reduzido, pois além de não possuir controlador de corrente (rápido), a eliminação do multiplicador é muito conveniente para programação em ponto fixo. Os

controladores CUC existentes são analógicos e se baseiam no uso de um integrador de tensão com *reset* para gerar uma portadora dente-de-serra com amplitude modulada (LAI, 1997).

Figura 2.1: Integrador de tensão com reset.

Alguns trabalhos atuais estão analisando a estratégia CUC com implementação digital não apenas para conversores chaveados, mas também para aplicações em acionamento de máquinas elétricas. Em (LOCK, 2012) é proposta uma nova estratégia para o controle do torque e do fluxo magnético de motores de indução através da técnica CUC. O controle digital foi implementado em DSP. Esta nova técnica supera alguns problemas encontrados no método convencional de controle direto do torque (DTC, direct torque control), tais como, operação em frequência variável, distorção da corrente, do fluxo e do torque.

Apesar de a técnica CUC ter sido bem investigada com relação aos conversores estáticos, (LIQIAO, 2009) propõem a aplicação em conversores *ac choppers* monofásicos. Tais conversores são amplamente utilizados em aplicações industriais, tais como, aquecedor industrial, partida suave de motores de indução e controle de velocidades de bombas. No controle desse conversor, muitas vezes, são utilizados valores instantâneos da tensão para o controlador proporcinal-integrativo (PI), este é o motivo pelo qual a resposta do sistema tem uma má dinâmica e distorção na tensão de saída quando há cruzamento por zero. Sabendo que a estratégia CUC é uma técnica não linear, a qual tem rápida resposta no transitório e um bom desempenho no monitoramento de controle, os autores perceberam que esta seria uma solução viável para o problema. Os mesmos comprovaram, com resultados experimentais e de simulação, que esta técnica é uma boa solução para o problema.

Em (JAPPE; MUSSA, 2011) foi apresentada uma análise que mais se assemelha ao que esta dissertação se propõe a fazer. Esta análise consiste na implementação em FPGA de um controlador baseado na estratégia CUC aplicado a um conversor *boost* monofásico, para correção de fator de potência. Os autores realizaram

dois trabalhos, um com apenas a validação simulacional e o outro para comprovação com resultados experimentais. Porém, assim como a grande maioria dos projetos propostos, os autores aplicaram seus sistemas de controle para apenas um tipo de conversor.

Os principais estudos sobre a técnica CUC são quase que exclusivamente, voltados para conversores estáticos. Por outro lado, os pesquisadores tentam cada vez mais preencher as lacunas na literatura no que diz respeito à implementação digital desta técnica. Percebeu-se, nesta seção, a quantidade de vantagens provenientes desta técnica e que apesar de haver bastantes trabalhos referentes ao CUC aplicados a várias topologias, ainda existem peculiaridades a serem estudadas, principalmente quando o controle é implementado digitalmente, indo mais além, quando são utilizados dispositivos FPGAs para implementação do mesmo. Neste sentido, este trabalho tenta contribuir de forma a analisar uma gama de topologias através do controle utilizando FPGA. As demais referências sobre a técnica de controle de um ciclo serão analisadas no decorrer da dissertação.

#### 2.3 Síntese do Capítulo

Apresentou-se neste capítulo um resumo dos principais trabalhos encontrados na literatura relacionados ao tema dessa dissertação. Inicialmente, abordaram-se os trabalhos que utilizam o controle digital para aplicações em eletrônica de potência, mostrando o avanço do controle de acordo com a evolução tecnológica e posteriormente apresentou-se os trabalhos que implementaram analogicamente e digitalmente a técnica de controle de um ciclo.

O próximo capítulo tem por objetivo realizar uma análise matemática e descrever as principais características das topologias de retificadores utilizadas neste trabalho, assim como apresentar a estratégia de controle de um ciclo.

# Capítulo 3

# Retificadores Boost Bidirecionais

Os retificadores *boost* bidirecionais estudados nesse capítulo são caracterizados pela topologia, pela estratégia de controle adotada e pelo projeto do controlador. Tais retificadores possuem como característica principal uma corrente de entrada proporcional à tensão de entrada, o que resulta em operação com fator de potência unitário. As estratégias de controle empregadas são obtidas com a técnica de controle de um ciclo (CUC); por fim é apresentado deduzido um modelo do retificador *boost* para projeto do controlador (PI).

#### 3.1 Topologias

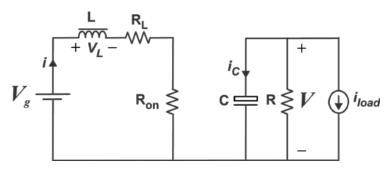

Os retificadores *boost* bidirecionais são amplamente utilizados para operação com correção do fator de potência (CFP) unitário. Estes retificadores operam em vários modos dependendo da topologia e do tipo de modulação de tensão aplicado. Em aplicações monofásicas, estes retificadores são comumente compostos por uma ponte completa, ou meia ponte, controlada. Sendo o sado *ca* conectado à rede através de uma indutância, utilizada para a imposição de uma forma de onda da corrente, e o lado *cc* é conectado a um banco de capacitores de alta capacidade em paralelo com a carga (BENTO, 2009).

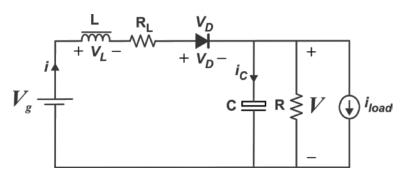

Este trabalho considera um total de seis modos de operações, obtidos pela combinação de quatro topologias e três modos de modulação de tensão. A escolha do modo de operação é determinada pelos requisitos das aplicações. As quatro topologias, mostradas na Figura 3.1, são: Retificador *boost* ponte completa; Retificador *boost* meia ponte; Retificador *boost* ponte completa intercalado; Retificador *boost* meia ponte intercalado. Os três tipos de modulação de tensão apresentam as seguintes características: no MBT a tensão de linha  $v_L$  assume valores positivos e negativos; no

MUT a tensão de linha  $v_L$  assume valores positivos ou negativos e zero; e, no MGT a tensão de linha  $v_L$  assume valores positivos ou negativos e zero porém, um dos braços opera em alta frequência enquanto o outro braço opera na frequência da rede, conforme ilustra a Figura 3.2. Assim, as seis possibilidades são:

- CFP1: Retificador *boost* para CFP em ponte completa com MBT.

- CFP2: Retificador *boost* para CFP em ponte completa com MUT.

- CFP3: Retificador *boost* para CFP em ponte completa com MGT.

- CFP4: Retificador *boost* para CFP em ponte completa intercalado com MGT.

- CFP5: Retificador *boost* para CFP em meia ponte com MBT.

- CFP6: Retificador *boost* para CFP em meia ponte intercalada com MBT.

Figura 3.1: Topologias CFP Boost. (a) CFP Boost ponte completa; (b) CFP Boost meia ponte; (c) CFP Boost ponte completa intercalada e (d) CFP Boost meia ponte intercalada.

Figura 3.2: Possíveis modulações de tensão para o inversor de tensão em ponte completa. (a) Inversor de tensão em ponte completa, (b) MBT aplicada nas opções CFP1, CFP5 e CFP6; (c) MUT, aplicada na opção CFP2; e (d) MGT, nas opções CFP2 e CFP4.

#### 3.1.1 Função de Transferência dos Retificadores Estudados

A função de transferência de quase regime permanente para todas as seis opções de retificadores é definida pela equação (3.1), desenvolvidas em (RAJAGOPALAN; LEE; NORA, 1999) e são mostradas na tabela 3.1. Elas são calculadas durante um período de chaveamento a partir das variações de corrente no indutor.

$$v_G = f(d)E (3.1)$$

Onde  $v_G$  é a tensão da rede; E é a tensão do barramento CC; f(d) é a função de transferência de estado quase estacionário do conversor, dada na tabela 3.1. Onde  $sign(v_G) = \pm 1$ , e um indicador unitário de fase para tensão da rede;  $d = t_{off}/T_S$ , e representa o ciclo de trabalho (Duty cycle). Se a frequência de chaveamento  $f_S$  for muito maior que a frequência da rede  $f_G$ , pode-se considerar que a variação de corrente num período de chaveamento é nula.

#### 3.1.2 Ondulação da Corrente de Entrada

A ondulação de corrente discutida aqui se refere às ondulações que inerentes a frequência de chaveamento ou múltiplos desta. A Figura 3.3 representa a forma de

onda da corrente de entrada para os seis opções de CFP. Consideraram-se iguais os tamanhos totais dos indutores para todas as opções do preestabelecidas. No caso dos intercalados, opções CFP5 e CFP6, a indutância L1 é igual à indutância L2, cujo valor é duas vezes a indutância do respectivo retificador de uma única célula,  $L_{I, 2} = 2L$ , ver Figura 3.1 (CHAN; ZHAO; QIANG; NENG, 2002).

| Opção | Função de transferência                        |

|-------|------------------------------------------------|

| CFP1  | $\frac{E}{v_G} = \frac{1}{(1 - 2d)}$           |

| CFP2  | $\frac{E}{v_G} = \frac{1}{(1 - 2d)}$           |

| CFP3  | $\frac{E}{v_G} = \frac{2}{1 + sign(v_G) - 2d}$ |

| CFP4  | $\frac{E}{v_G} = \frac{2}{(1 - 2d)}$           |

| CFP5  | $\frac{E}{v_G} = \frac{2}{(1 - 2d)}$           |

| CFP6  | $\frac{E}{v_G} = \frac{2}{1 + sign(v_G) - 2d}$ |

Tabela 3.1: Função de transferência de regime quase permanente.

Na operação com MBT é preciso o uso de indutores com grande volume para reduzir os esforços de corrente nas chaves e também para reduzir a ondulação da corrente de entrada. Estas ondulações ocorrem principalmente nas extremidades do semiciclo da rede. Para a eliminação da ondulação da corrente de entrada é possível utilizar o MGT. Esta modulação trabalha com grampeamento de  $180^{\circ}$ , sendo que um braço é comandado na frequência de chaveamento (alta frequência -  $f_S$ ), e o outro braço opera na frequência da rede,  $f_G$ . Porém sua ondulação de corrente é duas vezes maior do que a apresentada pela opção MUT.

#### 3.2 Controle

De forma geral, a técnica de controle de um ciclo para correção de fator de potência tem como base a emulação de uma resistência pura  $R_e$  vista da rede. Para os retificadores isto significa uma resistência de entrada fixa, dada por  $R_e = V_G/I_G$  e um fator de potência unitário. Sabe-se que os conversores chaveados são intrinsecamente não lineares. Neste caso o melhor desempenho destes conversores é obtido quando é

empregada a eles uma técnica de controle não linear. Pelo fato da técnica de controle de um ciclo ser não linear é esperado que o resultado seja relativamente promissor. Nesta técnica, a relação entre a razão cíclica d e a variável de controle  $v_m$ , bem como a relação entre a corrente de entrada  $I_G$  e d, são ambas não lineares. Porém, a relação entre  $v_m$  e  $I_G$  é linear.

Figura 3.3: Formas de onda da corrente de entrada para índice de modulação m=0,9. (a) CFP1; (b) CFP2; (c) CFP3; (d) CFP4; (e) CFP5; (f) CFP6.

O retificador *boost* básico, Figura 3.1(a), comporta várias opções de controle de corrente (ROSSETTO, 1994), entre as quais se podem mencionar técnicas tradicionais como controle pela corrente de pico, controle por histerese de corrente e controle pela corrente média (CANESIN, 1996; ZHOU, 1992; NOON, 1997). Tais técnicas utilizam multiplicadores analógicos para produzir a referência de corrente necessária para a correção de fator de potência. Além disto, as duas primeiras técnicas introduzem distorções na corrente de entrada, enquanto a última requer uma investigação da natureza não linear do conversor para o projeto do controlador e um tratamento mais acurado do controle de corrente.

Neste contexto, a técnica de controle de um ciclo (CUC) tem sido muito importante para aplicações de qualidade de energia e uma extensa produção científica está disponível na literatura técnica (SCHWARZ, 1976). A técnica CUC, quando comparado a outras técnicas de controle, apresenta várias vantagens: supera as não linearidades em conversores chaveados, elimina a distorção de *crossover*, não utiliza nenhum sensor de tensão da rede e tem a estabilidade em uma ampla variação dinâmica (CHAN, 2002; HUA, 2003; QIAN, 2000). A técnica CUC tem sido comumente implementada por realização analógica para estruturas de eletrônica de potência (SMEDLEY, 1995) incluindo alguns daqueles CFP mostradas na Figura 3.1 (SMEDLEY, 2001; QIAO, 2004; BENTO, 2006; RAJAPOPALAN, 1999).

A fim de emular uma resistência pura na entrada do retificador a técnica CUC para correção do fator de potência impõe uma linearidade entre  $v_m$  e  $I_G$  (SCHWARZ, 1976; SMEDLEY, 2001), o que resulta em um fator de potência da rede próximo do valor unitário. Para aplicações de CFP, esta técnica controla a magnitude da corrente de entrada através da variação da amplitude da portadora, que é definido pelo controlador de tensão do barramento CC, conforme ilustrado na Figura 3.4. Uma vez que o sinal de corrente é injetado diretamente no bloco PWM, Figura 3.6, a técnica CUC supera os problemas como o processamento do sinal de corrente (CHAN; ZHAO; QIANG; NENG, 2002), além de apresentar apenas dois sensores (corrente de entrada e tensão de saída). Esta técnica é mais simples do que as estratégias clássicas de controle, Figura 3.5, que emprega um multiplicador e um rápido controlador de corrente (malha interna de controle), e também necessita de detecção da tensão da rede para compor a corrente de referência da rede.

A análise e síntese da estratégia CUC é baseada na função de transferência de quase

regime permanente que é válida para um período de comutação  $T_S$ . Considerando o caso monofásico, a função de transferência relação generalizada do conversor é dada pela equação (3.1). Sendo assim, para a obtenção das leis de controle da técnica CUC são obtidas pela substituição de  $v_G$  por  $i_G$  na função de transferência de estado quase estacionário, tabela 3.1. As leis de controle para as combinações CFP1, CFP2, CFP3, CFP4, CFP5 e CFP6 são dadas pela tabela 3.2.

Figura 3.4: Esquema da técnica CUC para o controle de corrente.

Figura 3.5: Esquema da técnica de controle clássica para o controle de corrente.

Figura 3.6: Sinais de entrada do bloco PWM. Corrente de entrada senoidal e forma de onda das portadoras. Primeiro gráfico: MBT and MUT. Segundo gráfico: MGT.

As possibilidades CFP2, CFP4 e CFP6 utilizam duas portadoras, sendo a primeira defasada 180° da segunda, onde cada portadora é aplicada a um braço do retificador. É importante também resaltar que o controle de corrente para as opções intercaladas CFP4 e CFP6 é realizado separadamente para cada indutor do braço intercalado do *boost*, com o intuito de manter as correntes nos indutores iguais, com isso faz-se necessários a utilização de dois sensores de corrente.

| Opção | Lei de Controle                                                           |

|-------|---------------------------------------------------------------------------|

| CFP1  | $\bar{i}_G = (1 - 2d) \frac{E}{R_e}$                                      |

| CFP2  | $\bar{i}_G = (1 - 2d) \frac{E}{R_e}$                                      |

| CFP3  | $\bar{i}_G = \frac{1}{2} \left[ 1 + sign(v_G) - 2d \right] \frac{E}{R_e}$ |

| CFP4  | $\bar{i}_G = \frac{1}{2}(1 - 2d)\frac{E}{R_e}$                            |

| CFP5  | $\bar{i}_G = \frac{1}{2}(1 - 2d)\frac{E}{R_e}$                            |

| CFP6  | $\bar{i}_G = \frac{1}{2} \left[ 1 + sign(v_G) - 2d \right] \frac{E}{R_e}$ |

Tabela 3.2: Leis de controle da técnica CUC.

#### 3.3 Modelo

Com o intuito de simplificar o entendimento dos retificadores bidirecionais, o estudo apresentado nesta seção é feito para o retificador *boost* unidirecional monofásico ilustrado na Figura 3.7. Que, na operação como corretor de fator de potência, possui como característica principal uma corrente de entrada proporcional à tensão de entrada. Nesta estrutura podem-se reconhecer dois estágios: o estágio retificador e o estágio conversor. Primeiramente será estudado o estágio conversor, realizando a modelagem matemática do mesmo a fim de obter a sua função de transferência.

O estágio conversor *cc-cc* pode ser observado em cascata com o estágio retificador. Este estágio consiste em conversor *boost*, que é um circuito eletrônico elevador de tensão utilizado para converter uma tensão contínua não controlada em uma tensão contínua controlada de maior valor que a entrada. O conversor *boost* é um

conversor chaveado, muito comum em fontes chaveadas, ele consiste basicamente em um diodo, um indutor e uma chave, mais comumente caracterizada por um transistor, que pode ser do tipo, MOSFET, IGBT, BJT, etc. Na Figura 3.8 é mostrada a estrutura simplificada do conversor *boost*, onde podem ser observadas as seguintes características:

- Tensão de saída constante;

- Tensão de entrada variável, obtida a partir de uma ponte retificadora;

- Conversor controlado em corrente.

A consideração de uma tensão constante na saída permite o estudo da malha de corrente na entrada do conversor *boost*. Isto se consegue através do projeto de um filtro de saída para baixa frequência e uma malha externa de tensão, a qual apresentará uma dinâmica mais lenta que a malha de corrente para evitar a influência nesta última (LARICO, 2007). Para realização do controle de corrente e tensão é necessário conhecer o comportamento do conversor, para isto, a próxima seção mostra a modelagem do conversor *boost*.

Figura 3.7: Estrutura simplificada do retificador boost monofásico unidirecional.

Figura 3.8: Estrutura simplificada conversor boost.

### 3.3.1 Modelagem do Conversor Boost

Para obtenção da função de transferência do conversor *boost* é necessário a análise do mesmo considerando seu comportamento quando a chave está conduzindo e também quando a mesma está bloqueada, vale salientar que esta análise considera o conversor operando apenas no modo de condução contínuo. A modelagem realizada nesta seção levará em consideração as perdas nos dispositivos semicondutores e na resistência do enrolamento do indutor. Todas as variáveis estão caracterizadas na Figura 3.8, apresentada na seção anterior.

### 3.3.1.1 Chave em Condução

No momento em que a chave estiver em condução, o circuito equivalente momentâneo será representado pela Figura 3.9, onde a fonte de corrente  $i_{Load}$  caracterizará perturbações na carga do conversor.

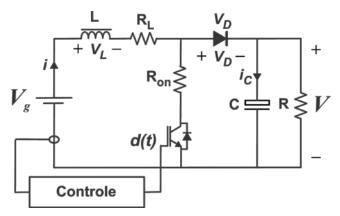

Figura 3.9: Circuito equivalente em modo de condução.

Aplicando a lei de Kirchhoff das tensões (LKT) na primeira malha do circuito obtém-se:

$$V_{q} - V_{L} - (R_{L} + R_{on}). i = 0. (3.2)$$

Sabe-se que a queda de tensão no indutor é dada por:

$$V_L = L \cdot \frac{di}{dt}. (3.3)$$

Substituindo (3.3) em (3.2) e isolando di/dt acha-se a equação (3.4).

$$\frac{di}{dt} = \frac{V_g}{I_c} - \left(\frac{R_L + R_{on}}{I_c}\right) \cdot i. \tag{3.4}$$

Aplicando a lei de Kirchhoff das correntes (LKC) na segunda malha do circuito obtémse a equação (3.5):

$$i_c + \frac{v}{R} + i_{load} = 0.$$

(3.5)

Sabendo que a corrente no capacitor é dada por (3.6).

$$i_c = C \cdot \frac{dv}{dt}. \tag{3.6}$$

Substituindo (3.6) em (3.5) e isolando o termo dv/dt acha-se a equação (3.7).

$$\frac{dv}{dt} = -\frac{v}{RC} - \frac{i_{load}}{C}. (3.7)$$

Considerando (3.2)-(3.5), as equações de diferenças que descrevem o conversor no modo de condução são representadas por (3.8).

$$\begin{cases} \frac{di}{dt} = \frac{V_g}{L} - \left(\frac{R_L + R_{on}}{L}\right) \cdot i \\ \frac{dv}{dt} = -\frac{v}{RC} - \frac{i_{load}}{C} \end{cases}$$

(3.8)

Representando estas equações na forma matricial, se obtém:

$$\begin{bmatrix} \frac{di}{dt} \\ \frac{dv}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{(R_L + R_{on})}{L} & 0 \\ 0 & -\frac{1}{RC} \end{bmatrix} \cdot \begin{bmatrix} i \\ v \end{bmatrix} + \begin{bmatrix} \frac{1}{L} & 0 & 0 \\ 0 & 0 & -\frac{1}{C} \end{bmatrix} \cdot \begin{bmatrix} V_g \\ V_D \\ i_{load} \end{bmatrix}.$$

(3.9)

### 3.3.1.2 Chave em Corte

Quando a chave estiver em corte, o circuito equivalente momentâneo será representado pela Figura 3.10.

Figura 3.10: Circuito equivalente com chave bloqueada.

Aplicando a LKT na primeira malha do circuito obtém-se:

$$V_g - V_L - v - R_L * i - V_D = 0. (3.10)$$

Substituindo (3.3) em (3.10) e isolando o termo di/dt:

$$\frac{di}{dt} = \frac{V_g}{L} - \frac{v}{L} - \frac{R_L}{L} \cdot i - \frac{V_D}{L}.$$

(3.11)

Aplicando a LKC no nó positivo da tensão no capacitor.

$$i_c + \frac{v}{R} + i_{load} = i. ag{3.12}$$

Substituindo (3.6) em (3.12) e isolando o termo dv/dt.

$$\frac{dv}{dt} = \frac{i}{C} - \frac{v}{RC} - \frac{i_{load}}{C}.$$

(3.13)

Considerando (3.10)-(3.13), as equações de diferença que representa o comportamento do conversor com a chave fechada são dadas por:

$$\begin{cases} \frac{di}{dt} = \frac{V_g}{L} - \frac{v}{L} - \frac{R_L}{L} \cdot i - \frac{V_D}{L} \\ \frac{dv}{dt} = \frac{i}{C} - \frac{v}{RC} - \frac{i_{load}}{C} \end{cases}$$

(3.14)

A representação na forma matricial de (3.14) é dada por:

$$\begin{bmatrix} \frac{di}{dt} \\ \frac{dv}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{R_L}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix} \cdot \begin{bmatrix} i \\ v \end{bmatrix} + \begin{bmatrix} \frac{1}{L} & -\frac{1}{L} & 0 \\ 0 & 0 & -\frac{1}{C} \end{bmatrix} \cdot \begin{bmatrix} V_g \\ V_D \\ i_{load} \end{bmatrix}.$$

(3.15)

### 3.3.2 Linearização do Modelo

As equações (3.9) e (3.15) podem ser representadas por espaço de estado, como determinado em (3.16).

$$\dot{X} = A \cdot X + B \cdot U. \tag{3.16}$$

Onde:

$$\dot{X} = \begin{bmatrix} \frac{di}{dt} \\ \frac{dv}{dt} \end{bmatrix}$$

,  $X = \begin{bmatrix} i \\ v \end{bmatrix}$  e U é a matriz de entrada.

Como existem duas matrizes A e B na análise, uma para cada situação da chave, adota-se por padrão as matrizes  $A_0$  e  $B_0$  para o momento em que a chave está bloqueada e  $A_1$  e  $B_1$  para o caso em que a chave está em condução. Define-se também uma nova variável  $\delta$  para indicar o estado da chave, se  $\delta=1$  a chave está em condução e se  $\delta=0$  a chave está bloqueada. Deste modo, as equações de estado podem ser reescritas como:

$$\dot{X} = (A_0 + \delta.(A_1 - A_0)).X + (B_0 + \delta.(B_1 - B_0)).U.$$

(3.17)

Obtendo o valor médio de (3.17), tem-se:

$$\langle \dot{X} \rangle = (A_0 + d \cdot (A_1 - A_0)) \cdot \langle X \rangle + (B_0 + d \cdot (B_1 - B_0)) \cdot \langle U \rangle.$$

(3.18)

Onde o termo  $\langle \dot{X} \rangle$  indica o valor médio de  $\dot{X}$  dentro de um ciclo de chaveamento. Realizando a linearização em torno do ponto de operação.

$$\begin{cases}

d = D + \hat{d} \\

< X > = x + \hat{x} \\

< U > = u + \hat{u}

\end{cases}$$

(3.19)

A equação (3.19) indica que os valores médios das grandezas podem ser escritos como um valor constante mais uma variação, representando uma perturbação. Substituindo (3.19) em (3.18) e rearranjando os termos encontra-se a seguinte equação:

$$\langle \dot{X} \rangle = \left[ A_0 + D \cdot (A_1 - A_0) + \hat{d} \cdot (A_1 - A_0) \right] * x +$$

$$+ \left[ A_0 + D \cdot (A_1 - A_0) + \hat{d} \cdot (A_1 - A_0) \right] \cdot \hat{x} +$$

$$+ \left[ B_0 + D \cdot (B_1 - B_0) + \hat{d} \cdot (B_1 - B_0) \right] \cdot \hat{u} +$$

$$+ \left[ B_0 + D \cdot (B_1 - B_0) + \hat{d} \cdot (B_1 - B_0) \right] \cdot \hat{u}.$$

(3.20)

Reorganizando a equação, colocando as varáveis em evidência, chega-se em (3.21).

$$\langle \dot{X} \rangle = [A_0 + D. (A_1 - A_0)]. \hat{x} +$$

$$+[(A_0 + A_0). x + (B_1 - B_0). u] * \hat{d} +$$

$$+[A_0 + D. (A_1 - A_0)]. x +$$

$$+[B_0 + D. (B_1 - B_0)]. u +$$

$$+(A_1 - A_0). \hat{d}. \hat{x} + (B_1 - B_0). \hat{d}. \hat{u}.$$

(3.21)

A equação (3.21) apresenta um modelo mais complexo do comportamento do conversor *boost*. Como se pode perceber o modelo abrange os efeitos de segunda ordem representados pelos fatores  $\hat{d} * \hat{x}$  e  $\hat{d} * \hat{u}$ . Porém neste trabalho não serão considerados os efeitos de segunda ordem, uma vez que as perturbações são mínimas. De acordo com a equação (3.19), pode-se chegar em (3.22), onde  $\langle \dot{X} \rangle$  é igual a  $\dot{\hat{x}}$ , já que a derivada de uma constante é zero.

$$<\dot{X}> = \frac{d()}{dt} = \frac{d(x+\hat{x})}{dt} = \frac{d(x)}{dt} + \frac{d(\hat{x})}{dt} = \dot{\hat{x}}.$$

(3.22)

Retirando então os termos de segunda ordem e substituindo (3.22) em (3.21), chega-se no modelo linearizado.

$$\dot{\hat{x}} = [A_0 + D. (A_1 - A_0)]. \hat{x} +

+ [B_0 + D. (B_1 - B_0)]. \hat{u} +

+ [(A_1 - A_0). x + (B_1 - B_0). u]. \hat{d} +$$

(3.23)

$$+[A_0 + D.(A_1 - A_0)].x +$$

$+[B_0 + D.(B_1 - B_0)].u.$

Fazendo,

$$A = [A_0 + D.(A_1 - A_0)] e B = [B_0 + D.(B_1 - B_0)],$$

(3.24)

E, substituindo em (3.23), obtêm-se:

$$\dot{\hat{x}} = A.\hat{x} + B.\hat{u} + [(A_1 - A_0).x + (B_1 - B_0).x + (B_1 - B_0).u].\hat{d} + A.x + B.u.$$

(3.25)

De acordo com (3.16) e sabendo que em regime permanente  $\dot{x}$ , que representa a condição de equilíbrio do sistema de controle em regime permanente. Logo, a equação (3.25) reduz-se a:

$$\dot{\hat{x}} = A.\,\hat{x} + B.\,\hat{u} + [(A_1 - A_0).\,x + (B_1 - B_0).\,u].\,\hat{d}. \tag{3.26}$$

Para chegar de forma simples na função de transferência do conversor no domínio da frequência (em Laplace) é conveniente reorganizar as equações:

$$[(A_1 - A_0).x + (B_1 - B_0).u] = M. (3.27)$$

E, substituindo em (3.26), chega-se na seguinte expressão:

$$\dot{\hat{x}} = A \cdot \hat{x} + B \cdot \hat{u} + M \cdot \hat{d} \implies \dot{\hat{x}} = A \cdot \hat{x} + \begin{bmatrix} B & M \end{bmatrix} \begin{bmatrix} \hat{u} \\ \hat{d} \end{bmatrix} \Longrightarrow$$

$$\implies \frac{d\hat{x}}{dt} = A \cdot \hat{x} + B_t \cdot \hat{u}_t. \tag{3.28}$$

Aplicando a transformada de laplace na equação anterior, fica-se com:

$$s. \hat{x}(s) = A. \hat{x}(s) + B_t \hat{u}_t(s) \implies \hat{x}(s) = (s.I - A)^{-1}.B_t \hat{u}_t$$

(3.29)

Na forma matricial:

$$\begin{bmatrix} \hat{i} \\ \hat{v} \end{bmatrix} \begin{bmatrix} F_{11}(s) & F_{12}(s) & F_{13}(s) \\ F_{21}(s) & F_{22}(s) & F_{23}(s) \end{bmatrix} \begin{bmatrix} \hat{v}_g \\ \hat{i}_{Load} \\ \hat{d} \end{bmatrix}.$$

(3.30)

Através da equação (3.30), sabe-se que a variação na tensão na carga é função direta de três parâmetros independentes:  $\hat{V}_g$ , as variações que ocorrem na tensão de entrada do conversor,  $\hat{d}$  as variações que ocorrem no ciclo de trabalho e  $\hat{\iota}_{Load}$  que representa as variações na carga. Então para controlar a tensão de saída devem-se analisar as variáveis, das quais a tensão depende:

$$G_{vd} = \frac{\hat{v}(s)}{\hat{d}(s)} \begin{vmatrix} \hat{v}_g = 0 \\ \hat{i}_{Load} = 0 \end{vmatrix}, G_{vg} = \frac{\hat{v}(s)}{\hat{v}_g(s)} \begin{vmatrix} \hat{d} = 0 \\ \hat{i}_{Load} = 0 \end{vmatrix}, Z_0 = \frac{\hat{v}(s)}{\hat{i}_{Load}(s)} \begin{vmatrix} \hat{v}_g = 0, \\ \hat{d} = 0 \end{vmatrix}$$

(3.31)

Onde  $Z_0$  é função de transferência que representa a impedância de saída do conversor,  $G_{vg}$  é a função de transferência da tensão de saída em relação à tensão de entrada e  $G_{vd}$  é a função de transferência da tensão de saída em relação à razão cíclica.

Concluída a etapa de modelagem e linearização do conversor *boost*, que representa o segundo estágio da estrutura do retificador, é possível realizar um estudo do sistema de controle para a corrente de entrada e tensão de barramento do retificador, a partir dos parâmetros da planta a ser controlada. Mas antes do projeto do sistema de controle é preciso conceituar rapidamente o outro estágio do retificador *boost* unidirecional, e assim analisar o comportamento do retificador *boost* bidirecional dando ênfase às quatro topologias inicialmente citadas neste trabalho.

### 3.4 Síntese do Capítulo

Neste capítulo apresentaram-se os conversores bidirecionais para os quais será aplicada a técnica de controle de um ciclo. Realizou-se também, a modelagem do retificador *boost* unidirecional monofásico afim facilitar o entendimento dos retificadores bidirecionais. As equações (3.29) e (3.31) serão utilizadas no próximo capitulo para obter a função de transferência do conversor, a fim de realizar o controle do barramento *cc*.

Apresentaram-se também as topologias de retificadores *boost* bidirecionais propostas para estudo (seis topologias), para as quais serão aplicadas estratégias de controle de ciclo seguindo uma implementação digital. A Figura 3.11 ilustra, de forma geral, o sistema de controle para as seis topologias apresentadas na seção 3.1. Vale salientar que a estrutura de controle apresentada considera as topologias operando apenas como retificadores, onde o usuário através da variável "Seletor de Modulação" pode escolher qual será a topologia a ser controlada. Percebe-se também que para as opções intercaladas, CFP4 e CFP6, é preciso monitorar a corrente em cada indutor, representada pelas variáveis "Modulate1 e 2". Um esquema global será apresentado posteriormente, de forma a abranger também os inversores.

Além disso, foi realizado um embasamento teórico da técnica CUC, explicitando suas principais vantagens, quando comparadas com as técnicas de controle de corrente convencionais.

Figura 3.11: Esquema geral do controlador unificado aplicado aos retificadores.

# Capítulo 4

# Concepção do Controlador Universal em FPGA

Este capítulo tem por objetivos detalhar o desenvolvimento do controlador unificado (SOARES, 2013), mostrando as principais características de cada bloco digital que compõe o controlador, incluindo o projeto e discretização do controlador do barramento cc, apresentar a ferramenta utilizada na concepção do projeto, bem como alguns resultados de simulação para validar o funcionamento teórico.

Como relatado na seção 1.2 o controlador unificado proposto pode ser aplicado a um total de doze conversores, sendo que seis deles são inversores de tensão e seis retificadores. Diante desta informação, é justificada a geração de um sinal senoidal de referência que possua as mesmas características da tensão da rede.

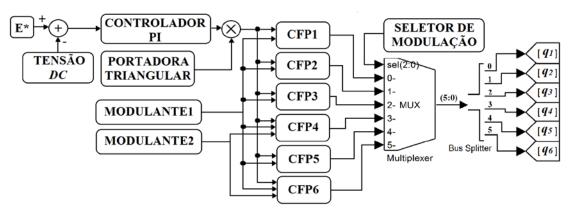

#### 4.1 DSP Builder

Todo o projeto descrito neste trabalho foi modelado utilizando a ferramenta DSP builder. O DSP builder toolflow é uma biblioteca para o Mathworks® Simulink desenvolvida pela Altera®. Esta biblioteca possibilita a integração em um único ambiente os fluxos de projeto do Matlab® e de FPGA, permitindo uma implementação simples e direta de algoritmos no ambiente simulink. A partir disto, esta ferramenta permite ao projetista desenvolver, testar, verificar e integrar o projeto em hardware, no simulink. Também é possível a integração e interação do circuito de controle com outras bibliotecas do simulink, tais como sistemas com elementos mecânicos e sistemas com estruturas de eletrônica de potência.

O DSP *builder* abstrai os detalhes de baixo nível da arquitetura de um projeto de FPGA, de modo que o projetista pode se concentrar no desenvolvimento de seus

algoritmos. Esta ferramenta também proporciona maior desempenho e menor latência da implementação de *hardware* para os engenheiros de controle e engenheiros industriais que não possuem experiência com o uso de linguagem de descrição de *hardware* (HDL) ou em desenvolvimento de projetos baseados em FPGA.

A biblioteca DSP *builder* da Altera® também se encarrega de algumas atribuições inerentes a concepções de projetos digitais, tais como, simulação dos algoritmos, conversão dos algoritmos para código HDL e finalmente a compilação do projeto, além de ser possível carregar e testar o projeto completo em *hardware*. Os arquivos gerados pela biblioteca podem ser, por exemplo, do tipo VHDL e *Verilog*, que são as linguagens de descrição de *hardware* mais conhecidas pelos projetistas. A Figura 4.1 ilustra o fluxo de projeto completo utilizando o DSP *Builder*.

Figura 4.1: Fluxo de projeto com o DSP Builder.

Na etapa de desenvolvimento, o próprio *simulink* do Matlab® é utilizado para elaborar os algoritmos, porém, as ferramentas utilizadas no desenvolvimento são apenas as que estão presentes na biblioteca DSP *builder*, se forem utilizados blocos de outros Toolbox que não sejam do DSP *builder*, estes não serão descritos em VHDL. Na elaboração de projetos utilizando a ferramenta DSP *Builder* podem ser utilizados os *Sinks* e *Sources* (Bibliotecas de componentes) do Toolbox do *simulink*, desde que os blocos utilizados sejam apenas para gerar sinais de entrada (*Sources*) e para monitorar os resultados intermediários e finais do modelo de construção (*Sinks*). A fase de implementação, caracteriza-se pela capacidade que a ferramenta DSP *Builder* tem de comunicar o ambiente de desenvolvimento Matlab® /*simulink* com a ferramenta de gravação em FPGA e o Quartus II. A última fase é a de verificação que se caracteriza pela análise dos sinais do *hardware* no próprio *simulink* (JÚNIOR, 2010).

A Biblioteca DSP Builder possui vários blocos funcionais, tais como blocos que implementam funções aritméticas, funções de armazenamento, funções para o processamento de números complexos e para interface com dispositivos de entrada e saída, como é ilustrada na Figura 4.2. Uma das grandes características desta biblioteca é fornecer funções complexas já implementadas como filtros FIR, osciladores NCO (*Numerically Controlled Oscillator*), e FFT (*Fast Fourier Transform*), entre outros. Nesta categoria de funções estão incluídas as funções complexas de DSP desenvolvidas pela Altera® e que podem ser incluídas no projeto de forma imediata, bastando configurar os parâmetros da função e adicioná-la ao projeto como um novo bloco.

Figura 4.2: Biblioteca DSP builder.